Read next

Welche Exponate werden auf der Xinjiang-Sicherheitsausstellung (CAESE) 2025 gezeigt?

Die mit Spannung erwartete Xinjiang Security Exhibition (CAESE) findet vom 11. bis 13. September 2025 im Xinjiang Intern...

Articles

2026-03-30

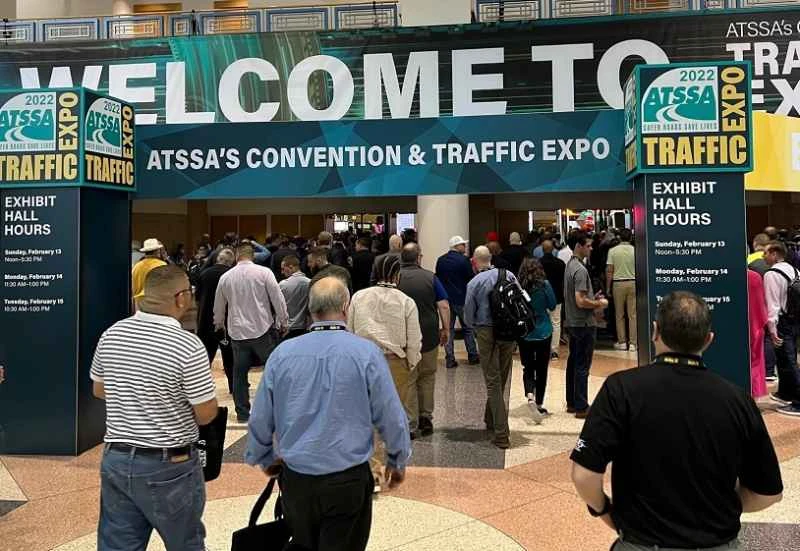

ATSSA Traffic Expo 2027 Ausstellerleitfaden (Zeit, Ort und Ticketkauf)

Articles

2026-03-30

Wie kann man Tickets für die Textilmesse Textile Asia 2026 in Pakistan kaufen?

Articles

2026-03-30